本系列专题聚焦于数字芯片物理实现(PR)后端流程,重点解析使用Cadence Innovus工具进行时钟树综合(Clock Tree Synthesis, CTS)的关键技术与实战方法。

内容系统全面,适合从事集成电路后端设计的工程师和高年级学生。

资料共128页,结构清晰,循序渐进地介绍PR后端布局布线的核心流程。

从Innovus的基本操作入手,逐步深入CTS阶段的约束设置、时钟网络构建、 skew优化、功耗控制及修复手段,帮助读者掌握从前端到物理实现的完整链路。

所有内容均来源于实际项目案例,结合常见问题与调试技巧,提供可复用的脚本模板与参数配置建议。

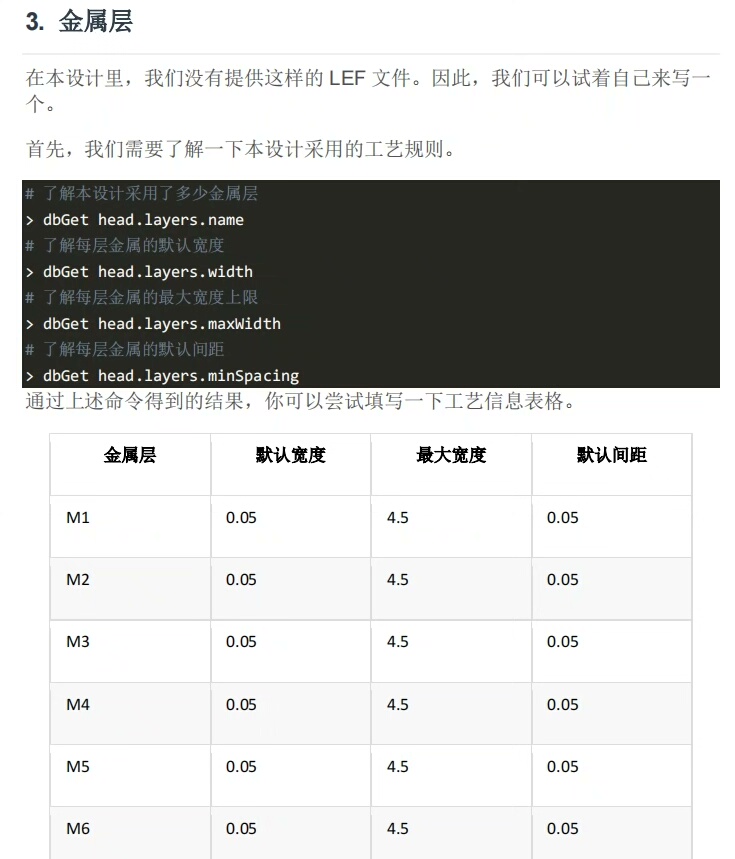

特别针对CTS后的时序收敛、拥塞管理、金属层分配等难点进行详细剖析,提升工程实践能力。

PDF文档包含丰富图表与截图,直观展示每一步操作流程。

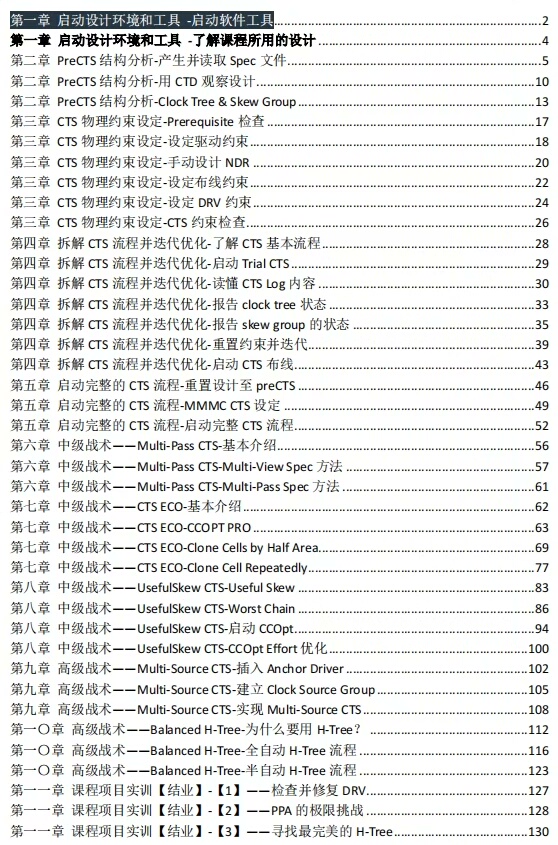

图二即为完整目录预览,涵盖章节包括:PR流程概览、Innovus环境搭建、CTS前准备、时钟架构设计、优化迭代策略、签核检查要点等,便于快速定位所需内容。

无论你是刚接触Innovus的新手,还是希望精进CTS技能的资深工程师,本资料都能为你提供实用指导。

通过系统学习,可显著提升芯片后端设计效率与质量,助力项目顺利流片。

发货方式

自动:在特色服务中标有自动发货的商品,拍下后,源码类 软件类 商品会在订单详情页显示来自卖家的商品下载链接,点卡类 商品会在订单详情直接显示卡号密码。

手动:未标有自动发货的的商品,付款后,商品卖家会收到平台的手机短信、邮件提醒,卖家会尽快为您发货,如卖家长时间未发货,买家也可通过订单上的QQ或电话主动联系卖家。

退款说明

1、源码类:商品详情(含标题)与实际源码不一致的(例:描述PHP实际为ASP、描述的功能实际缺少、功能不能正常使用等)!有演示站时,与实际源码不一致的(但描述中有"不保证完全一样、可能有少许偏差"类似显著公告的除外);

2、营销推广类:未达到卖家描述标准的;

3、点卡软件类:所售点卡软件无法使用的;

3、发货:手动发货商品,在卖家未发货前就申请了退款的;

4、服务:卖家不提供承诺的售后服务的;(双方提前有商定和描述中有显著声明的除外)

5、其他:如商品或服务有质量方面的硬性常规问题的。未符合详情及卖家承诺的。

注:符合上述任一情况的,均支持退款,但卖家予以积极解决问题则除外。交易中的商品,卖家无法修改描述!

注意事项

1、在付款前,双方在QQ上所商定的内容,也是纠纷评判依据(商定与商品描述冲突时,以商定为准);

2、源码商品,同时有网站演示与商品详情图片演示,且网站演示与商品详情图片演示不一致的,默认按商品详情图片演示作为纠纷评判依据(卖家有特别声明或有额外商定的除外);

3、点卡软件商品,默认按商品详情作为纠纷评判依据(特别声明或有商定除外);

4、营销推广商品,默认按商品详情作为纠纷评判依据(特别声明或有商定除外);

5、在有"正当退款原因和依据"的前提下,写有"一旦售出,概不支持退款"等类似的声明,视为无效声明;

6、虽然交易产生纠纷的几率很小,卖家也肯定会给买家最完善的服务!但请买卖双方尽量保留如聊天记录这样的重要信息,以防产生纠纷时便于送码网快速介入处理。

淘好品声明

1、作为第三方中介平台,依据双方交易合同(商品描述、交易前商定的内容)来保障交易的安全及买卖双方的权益;

2、平台上所有的资源都是亲测无误的,在平台下单安全有保障,有任何问题,可以随时联系在线客服。